520N-MX PCIe 卡,採用英特爾 Stratix 10 MX FPGA

PCIe FPGA 卡 520N-MX Stratix 10 FPGA 板,帶 16GB HBM2 用於加速記憶體受限應用的強大解決方案 需要報價?跳轉到定價表單

GROVF RDMA IP 核和主機驅動程式提供基於融合乙太網的 RDMA (RoCE v2) 系統實現以及與標準動詞 API 的整合。RDMA IP 隨參考設計一起提供,其中包括IP子系統本身、100G MAC IP子系統、DMA 子系統、主機驅動程式和軟體上的範例應用程式。系統驅動程式與 OFED 標準動詞 API 集成,並與著名的 RNIC 卡和軟體相容。該IP核還提供RoCE v2的低延遲 FPGA 實現,輸送量為100 Gbps。

該解決方案是實現基於融合乙太網協定的 RDMA 的軟 IP。它由整合了 MAC 和 DMA 的 FPGA IP 以及主機 CPU 驅動程式組成。該IP與BittWare的IA-840f和IA-420f FPGA卡相容,採用Altera Agilex 7,以及XUP-VV8和XUP-P3R FPGA卡,採用AMD UltraScale+。該解決方案符合 IB 規範中所述的通道適配器和 RoCE v2 要求。第 1 頁上的圖表顯示了系統的簡單體系結構概述。數據平面和可靠的通信是硬體卸載的,並且實現不包括FPGA中的CPU內核。

參考範例由三部分組成:

| 裝置 | LUT | 片上記憶體 |

|---|---|---|

| 超大規模+ VU9P | 170K | 6兆位元組 |

| Agilex 7 AGF014 | 170K | 6兆位元組 |

我們的技術銷售團隊隨時準備提供可用性和配置資訊,或回答您的技術問題。

“*”表示必填欄位

PCIe FPGA 卡 520N-MX Stratix 10 FPGA 板,帶 16GB HBM2 用於加速記憶體受限應用的強大解決方案 需要報價?跳轉到定價表單

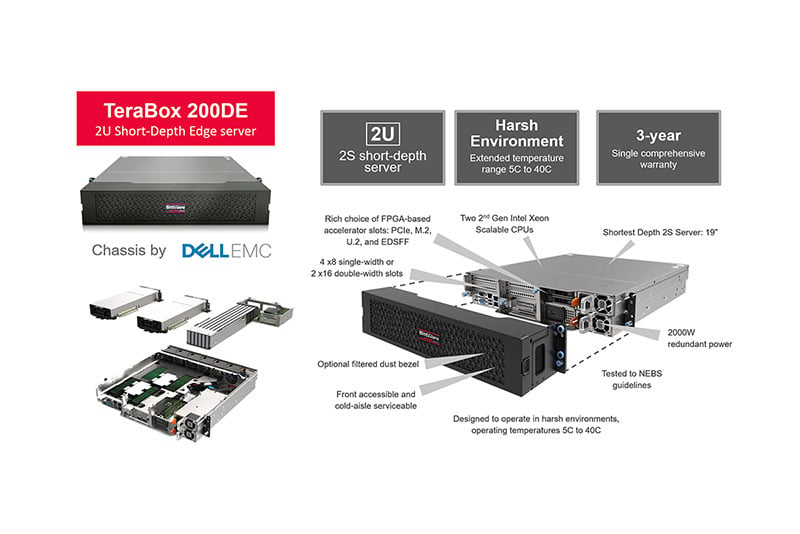

BittWare點播網路研討會企業級FPGA伺服器:TeraBox方法 基於FPGA的卡正在成熟為數據中心和邊緣計算的關鍵設備。但是,有一個