IPsec Extreme Speed IP Core

Go Back to IP & Solutions IPsec IP Core Extreme Speed IPsec IP Core IPsec (Internet Protocol Security) is a widely accepted and adopted security

VAS Suite from Megh Computing is an intelligent video analytics solution for security and system integrators who need actionable insights with enterprise class performance, while managing TCO considerations.

With Megh’s Concierge Support to help you get started with development, VAS Suite makes it easy to transition to AI-driven business operations. VAS Suite runs on BittWare cards with Altera Stratix 10 FPGAs with plans to support Altera Agilex FPGAs.

Review live and stored events

Adjust settings for highest accuracy

Rules and notifications

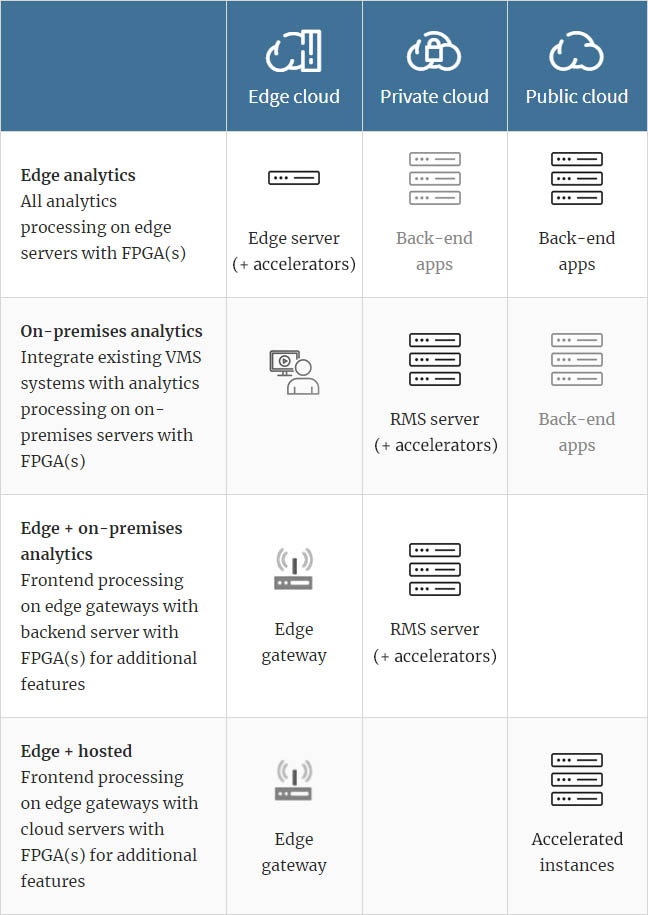

Deployment and integration options

Advanced configuration

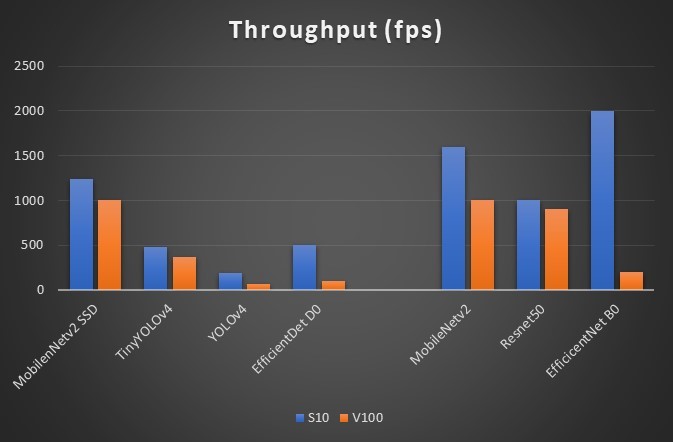

Performance numbers for the most common models running on Altera Stratix 10 compared to NVIDIA’s V100 GPUs

Provided with Core

Simulation tool used:

QuestaSim (contact IntelliProp for latest versions supported)

Support:

Phone and email support will be provided for fully licensed cores for a period of 6 months from the delivery date.

Notes:

Other simulators are available. Please contact IntelliProp for more information.

Enable real-time analytics at the edge, on premises, or private or public cloud.

VAS Suite offers video analytics for a variety of public safety and business operations use cases.

Watch a demo of the use cases.

High performance DL inferencing on FPGAs for

The Inferencing stage is the most critical stage of the pipeline implementing the deep learning models for object detection and image classification. Megh’s DLE (Deep Learning Engine) running on FPGAs delivers the best performance for many of the models used for IVA. The high throughput achieved with FPGAs delivers the lowest cost per stream for many of the IVA use cases.

Our technical sales team is ready to provide availability and configuration information, or answer your technical questions.

"*" indicates required fields

Go Back to IP & Solutions IPsec IP Core Extreme Speed IPsec IP Core IPsec (Internet Protocol Security) is a widely accepted and adopted security

White Paper FPGA-Accelerated NVMe Storage Solutions Using the BittWare 250 series accelerators Overview In recent years, the migration towards NAND flash-based storage and the introduction

Build ultra-low latency apps for fintech using Enyx off-the-shelf solutions and the nxFramework.

BittWare Partner IP Query Processing Unit (QPU) Build FPGA-powered accelerators to query, analyze or reformat stored or streaming data at PCIe Gen4 speeds! Eideticom’s Query