Comparing FPGA RTL to HLS C/C++ using a Networking Example

White Paper Comparing FPGA RTL to HLS C/C++ using a Networking Example Overview Most FPGA programmers believe that high-level tools always emit larger bitstreams as

Join BittWare and Intel as we look at oneAPI™ with a focus on FPGAs. We will look at a real-world 2D FFT acceleration example which utilizes the Intel® Stratix® 10 MX including HBM2 memory on BittWare’s 520N-MX card.

"*" indicates required fields

Craig Petrie

Craig Petrie David Clarke

David Clarke Maurizio Paolini

Maurizio Paolini Richard Chamberlain

Richard Chamberlain

White Paper Comparing FPGA RTL to HLS C/C++ using a Networking Example Overview Most FPGA programmers believe that high-level tools always emit larger bitstreams as

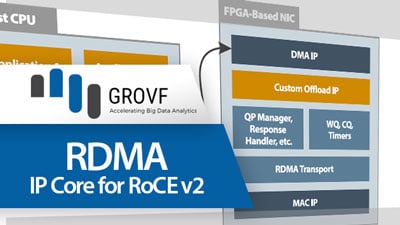

BittWare Partner IP Core RDMA Low-Latency RoCE v2 at 100Gbps The GROVF RDMA IP core and host drivers provide RDMA over Converged Ethernet (RoCE v2)

FPGA Server TeraBox 2102D 2U Server for FPGA Cards Legacy Product Notice: This is a legacy product and is not recommended for new designs. It

Explore using oneAPI with our 2D FFT demo on the 520N-MX card featuring HBM2. Be sure to request the code download at the bottom of the page!