IA-420f PCIe Accelerator with Intel Agilex FPGA

Introducing the IA-420f: A Powerful Low-Profile FPGA Card Powered by Intel Agilex Tap Into the Power of Agilex The new Intel Agilex FPGAs are more

The TimeServo IP core by Atomic Rules is an RTL IP core that serves the function of an FPGA’s system timer or clock. Although specifically designed to support the needs of line-rate independent packet timestamping, TimeServo may find use where there is the need for a high-resolution, modest-accuracy timebase. TimeServo and TimeServoPTP both use a digital phase locked loop (DPLL) to control the frequency of a Numerically Controlled Oscillator (NCO). A stable reference clock (whose absolute accuracy is not important) provides the clock for the NCO.

In conjunction with a timestamp-capable MAC (not included), TimeServo can be ordered as TimeServoPTP: a complete IEEE-1588v2/PTP ordinary slave device. TimeServoPTP does not require any host processor interaction to function.

All operation of the TimeServo is controlled though an AXI4-Lite Memory Mapped control-plane interface. A set of defined registers controls the module and returns the status. The control and status registers are always functioning when the control plane is operational.

In all cases, time is “made” from a Reference Clock signal. This reference clock should be chosen to be of the best possible stability. Its absolute frequency is less important when the digital PLL is engaged. The reference clock increments a 120-bit phase accumulator on each edge. Logic in the TimeServo DSP section statically or dynamically adjusts the fractional increment value added at each reference clock.

In the absence of an externally supplied Pulse-Per-Second (PPS) signal; TimeServo can be set, trimmed, and nudged under software control.

In the presence of an externally supplied PPS signal, the time can be set and nudged; but the frequency trim (e.g. faster/slower) is self-controlled and updated by TimeServo.

Supporting the trend of contemporary MACs having timestamp logic separated into multiple clock domains; each of the TimeServo’s outputs may each be placed in their own clock domain; and up to 32 outputs may be generated by the component when instantiated.the advantages of FPGA hardware acceleration.

TimeServo PTP has all of the TimeServo features listed above plus the following:

| Clock | Minimum (MHz) | Nominal (MHz)[1] | Maximum (MHz)[2] |

|---|---|---|---|

| axi_clk | 50 | 125 | 500 |

| ref_clk | 100 | 250 | 500 |

| now_clk_ | 50 | 312.5 | 500 |

[1] Performance Measurements made at nominal frequency

[2] FPGA performance limits may prevent operation at Maximum frequency (e.g. Timing Closure)

The TimeServo IP is compatible with all current BittWare cards with AMD UltraScale+, Intel Stratix 10 and Intel Agilex FPGAs.

The TimeServo IP is compatible with all current BittWare cards with Xilinx UltraScale+, Intel Stratix 10 and Intel Agilex FPGAs.

Our technical sales team is ready to provide availability and configuration information, or answer your technical questions.

"*" indicates required fields

Introducing the IA-420f: A Powerful Low-Profile FPGA Card Powered by Intel Agilex Tap Into the Power of Agilex The new Intel Agilex FPGAs are more

White Paper Introduction to BittWare’s SmartNIC Shell for Network Packet Processing Overview SmartNIC Shell is a complete working NIC that is implemented on a BittWare

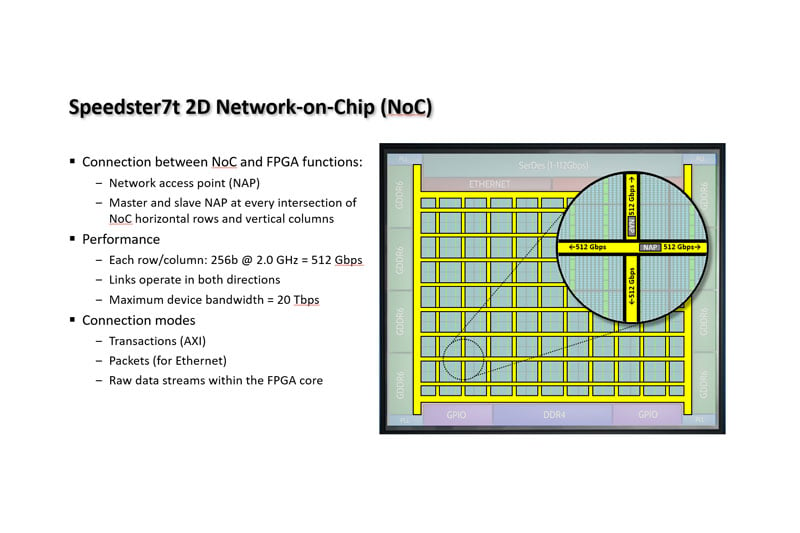

BittWare Webinar Introducing VectorPath S7t-VG6 Accelerator Card Now available on demand: In this webinar, Achronix® and Bittware will discuss the growing trends of using PCIe

PCIe FPGA Card XUP-VV8 UltraScale+ FPGA PCIe Board with 4x QSFP-DDs 8x 100GbE Network Ports and VU9P/13P FPGA Need a Price Quote? Jump to Pricing