Building BittWare’s Packet Parser, HLS vs. P4 Implementations

White Paper Building BittWare’s Packet Parser, HLS vs. P4 Implementations Overview One of the features of both BittWare’s SmartNIC Shell and BittWare’s Loopback Example is

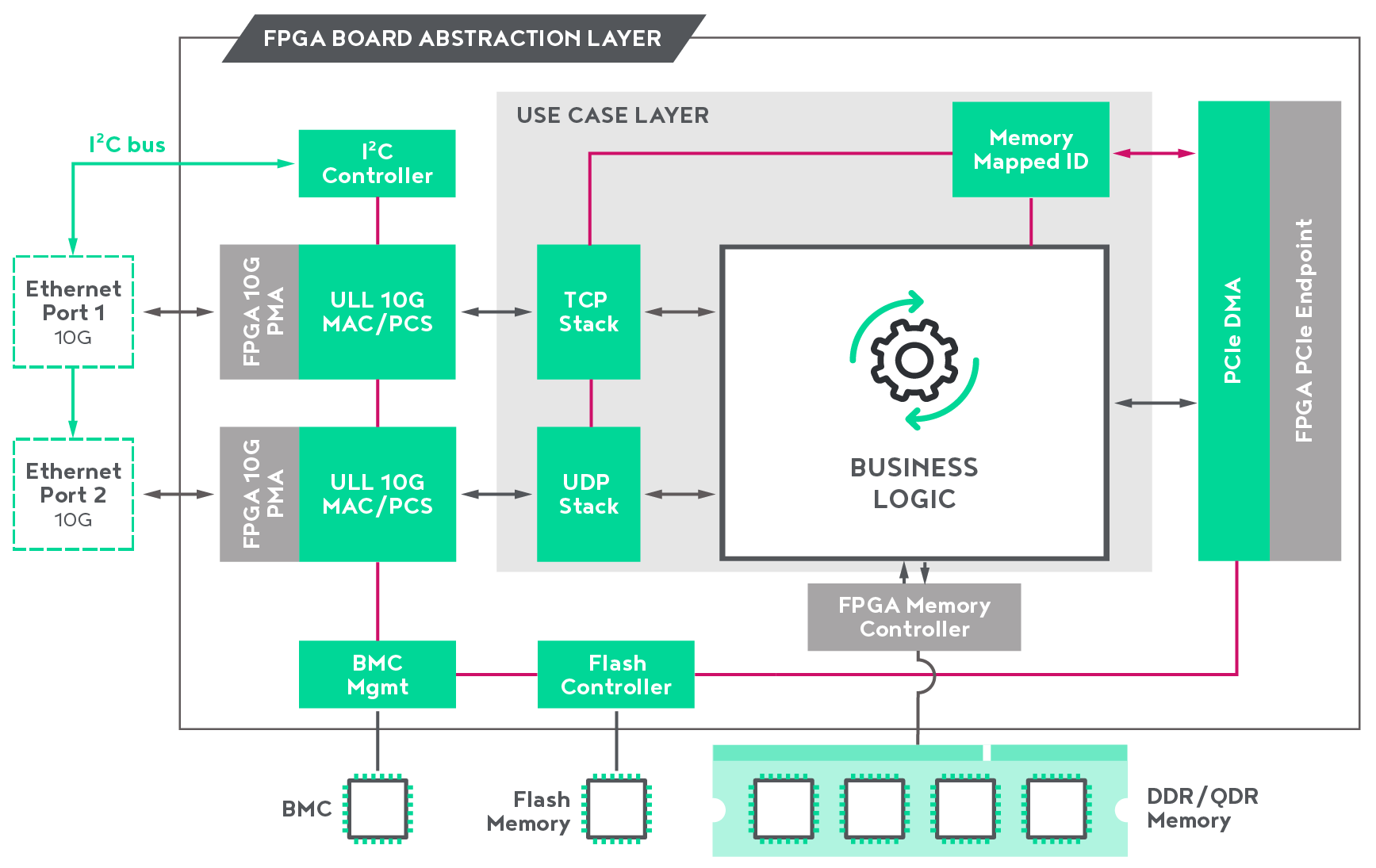

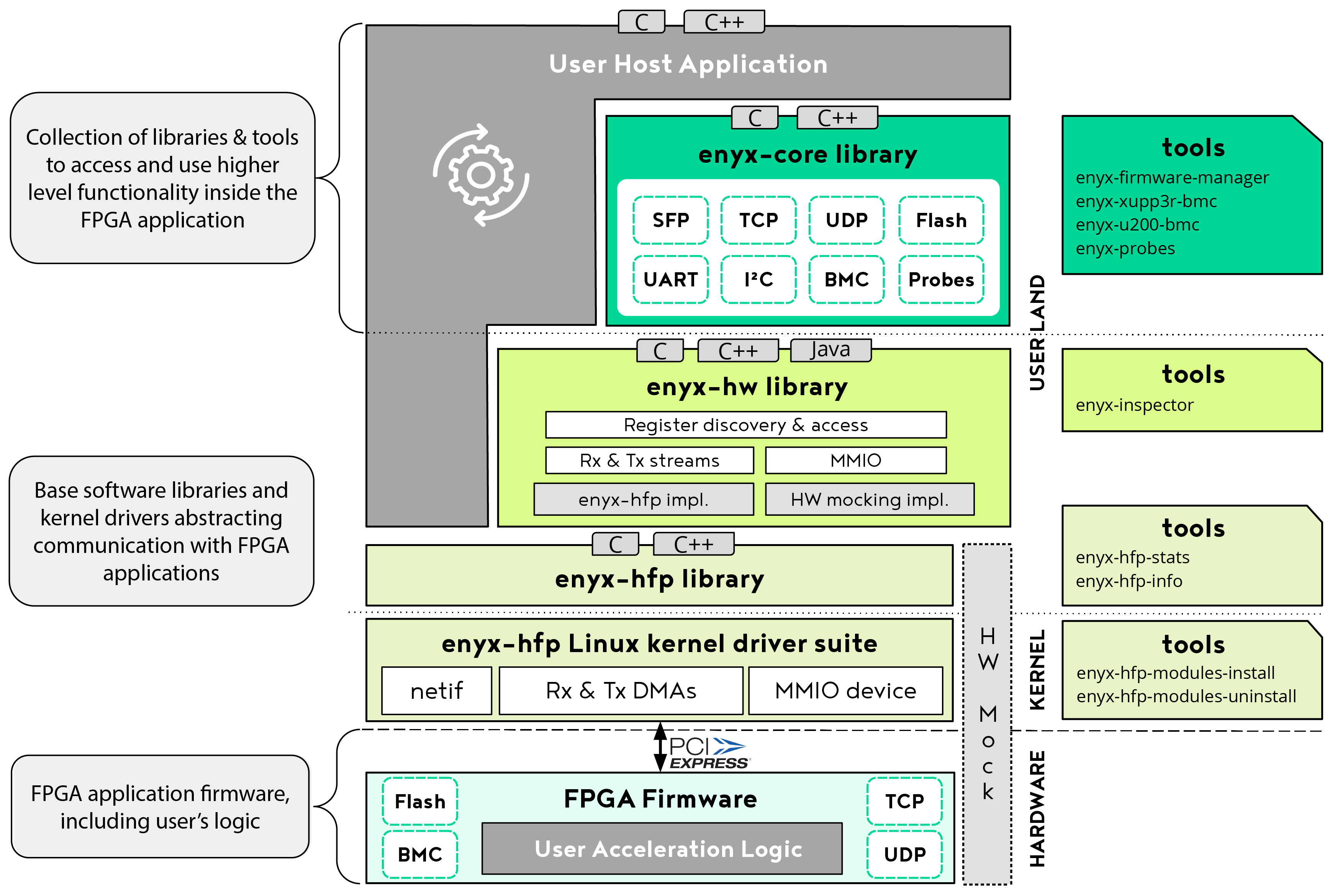

The Enyx Development Framework (nxFramework) is a hardware and software development environment designed to efficiently build and maintain ultra-low latency FPGA applications for the financial industry. Based on 10 years of research and development, nxFramework is the foundation for all Enyx off-the-shelf solutions and provides clients with the toolchain to manage a large portfolio of applications.

Developed for building in-house high performance trading engines, order execution systems, pre-trade risk check gateways, and custom projects — any skilled FPGA developer starting a new low latency project, maintaining an existing one, or looking to change platforms can immediately reduce their time-to-production with nxFramework.

Ultra-low latency connectivity cores

Library of 60+ utility cores

Provided with Core

Simulation tool used:

QuestaSim (contact IntelliProp for latest versions supported)

Support:

Phone and email support will be provided for fully licensed cores for a period of 6 months from the delivery date.

Notes:

Other simulators are available. Please contact IntelliProp for more information.

Enables simple configuration and monitoring of Enyx connectivity & utility cores, including interaction with the FPGA application via our C/C++ libraries.

A Python scripted development environment that enables users to simplify their development cycle and accelerate their time-to-production.

Equipped with a web-based GUI that can configure and monitor the FPGA at runtime, allowing for quick deployment and debug.

ULL Tick-to-trade platform

Pre-trade Risk Check Gateway

Our technical sales team is ready to provide availability and configuration information, or answer your technical questions.

"*" indicates required fields

White Paper Building BittWare’s Packet Parser, HLS vs. P4 Implementations Overview One of the features of both BittWare’s SmartNIC Shell and BittWare’s Loopback Example is

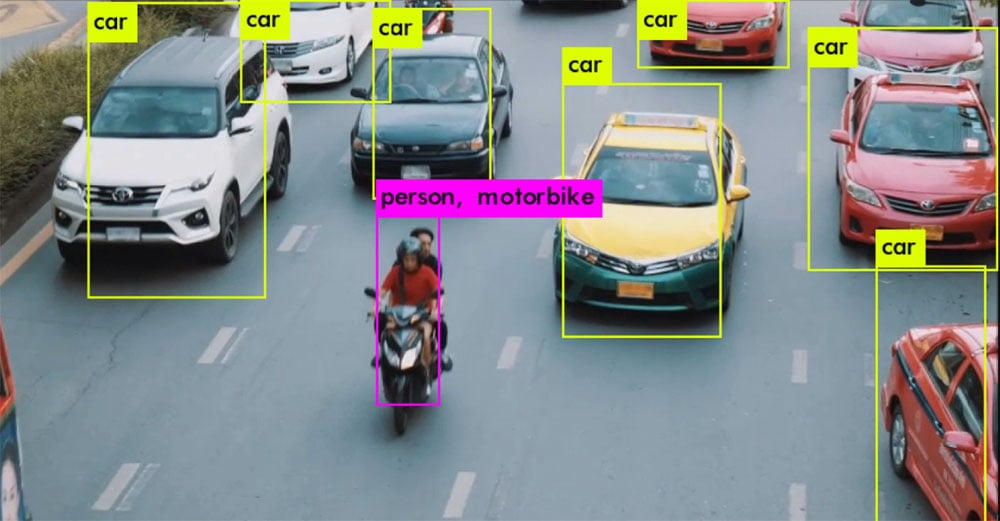

White Paper FPGA Acceleration of Binary Weighted Neural Network Inference One of the features of YOLOv3 is multiple-object recognition in a single image. We used

White Paper Introduction to BittWare’s SmartNIC Shell for Network Packet Processing Overview SmartNIC Shell is a complete working NIC that is implemented on a BittWare

Intel® oneAPI™ High-level FPGA Development Menu Evaluating oneAPI Accelerator Cards ASPs More Info Contact/Where to Buy Is oneAPI Right for You? You may already know