Arkville アトミックルールのDPDK IPコア

Atomic Rules社のPCIe Gen4データムーバーIPです。BittWareの PCIe Gen4 カードを使用して最大 220 Gb/s を達成し、標準 DMA よりも高い性能が必要な場合に開発チームの負担を軽減します。特徴DPDKおよびAXI規格、パケットやその他のデータフォーマットでの動作、最大400GbEまでのあらゆるラインレートでの動作。

世界の接続性がますます高まることで、増え続けるデータが生み出されています。機械学習は、正しく適用されれば、このデータ内のパターンや相互作用を抽出するように学習することができます。FPGAテクノロジーはその手助けをします。

機械学習は人工知能(AI)の一分野であり、アルゴリズムとデータを用いて、あるタスクを実行できるシステムを作成するものです。システムの精度は、より多くのデータを処理するにつれて徐々に向上します(学習と呼ばれます)。十分な精度が得られると、このシステムは訓練されたとみなされ、他の環境に配備されるようになります。ここで、同じ学習済みアルゴリズムを使用して、結果の統計的確率を推論することができる。これは推論と呼ばれる。

ニューラルネットワークは、ほとんどの機械学習タスクの基礎を形成しています。ニューラルネットワークは複数の計算層で構成され、その相互作用はトレーニング中に学習した係数に基づいています。 このホワイトペーパーでは、FPGAデバイスでのニューラルネットワークの推論に焦点を当て、その長所と短所を説明する。

のFPGAアクセラレータ製品を使用した畳み込みニューラルネットワークの高速化についてご覧ください。BittWare

OpenCLを使用して、YOLOv3機械学習フレームワークを当社のFPGAカードに適応させた方法をご紹介します。

ニューラルネットワークの中核をなすのは、膨大な数の掛け算の計算です。これらの計算は、何千ものニューロンの相互作用をシミュレートし、何かが発生する可能性を統計的に算出します。画像認識の場合、これはネットワークが特定の物体を観察しているという信頼性の要因になります。もちろん、間違っていることもあります。例えば、人間は無生物の中に人間の顔を見ることがよくあります!したがって、どのようなシステムであっても、誤った結果に対する一定の許容範囲が必要となります。このような結果の統計的性質は、最終的な答えがアプリケーションの許容範囲によって定義された満足のいく精度のレベルにとどまる限り、計算のダイナミックレンジを変化させる機会を提供します。その結果、推論では、使用するデータ型に工夫を凝らすことができる。

データ幅はしばしば8ビット整数に縮小でき、場合によっては1ビットにまで縮小できる。FPGAは、ほとんどすべてのサイズのデータ型を処理できるように構成でき、計算効率をほとんど損ないません。

ニューラルネットワークの推論に関して、ASIC、CPU、GPU、FPGAにはそれぞれメリットとデメリットがあります。カスタムチップ(ASIC)は最高のパフォーマンスと低コストを実現しますが、ターゲットとなるアルゴリズムにのみ対応し、柔軟性はありません。 一方、CPUはプログラミングの自由度が最も高いですが、計算スループットは低くなります。GPUの性能は通常、CPUよりもはるかに高く、大きなバッチ数、つまり多くのクエリを並行して処理する場合には、さらに向上します。レイテンシが重要なリアルタイムシステムでは、入力データをバッチ処理することができない場合があります。これはFPGAがややユニークである分野の1つで、ニューラルネットワークを1つのクエリに最適化しながら、高レベルの計算資源利用を達成することができます。ASICが存在しない場合、FPGAはレイテンシが重要なニューラルネットワーク処理に最適です。

図 1 は、FPGA の典型的なアクセラレータ・オフロード構成を示したものです。係数データは、接続されたディープDDRまたはHBMメモリにロードされ、ホストから転送されたデータを処理する際にAI推論エンジンによってアクセスされるように更新されます。GPUは通常、高いバッチ数でFPGAを上回りますが、小さなバッチサイズや低レイテンシーがシステムの重要な制約である場合は、FPGAが魅力的な選択肢となります。

図1:FPGA推論オフロード

FPGAが特に優れているのは、AI推論と他のリアルタイム処理要件を組み合わせることです。 FPGAのリコンフィギュラブルIOは、高速イーサネットからアナログセンサーデータまで、さまざまな接続性の問題に合わせてカスタマイズすることができます。このため、FPGAは、ASICが存在しないエッジで複雑な推論を実行できるユニークな存在となっています。また、デバイスは同じIOを使用して、アプリケーションに最適な構成で複数のFPGAを接続したり、既存のサーバー接続に適合させることができます。接続は特注品でも、イーサネットのような標準規格に準拠したものでも可能です。

図2 : データパイプラインライン内での推論の使用例

インライン処理の場合、ニューラルネットワークはラインレートでデータを処理できればよい。この場合、FPGAは希望するスループットに対応するために必要なリソースのみを使用し、それ以上は使用しません。これにより消費電力を節約し、暗号化など他のタスクのためにFPGAの実権を余らせることができます。

データプライバシーが重要視される分野では、機械学習の大きな機会がある。例えば、医療診断では、クラウドアクセラレーション の恩恵を受けることができる。しかし、患者データは機密性が高く、複数の施設に分散している。サイト間でやり取りされるデータは、少なくとも暗号化されていなければなりません。FPGAは、暗号化解除、AI処理、暗号化のすべてを非常に低いレイテンシーで行うことができます。重要なのは、復号化されたデータがFPGAの外に出ることがないことである。

図3:FPGAを用いて、クラウド上で復号化・暗号化ロジックによる推論を行う。

最終的には、このような機密データを処理するためには、FPGAが有望視されているホモモーフィック暗号化が望まれます。

ニューラルネットワークには様々な種類があります。最も一般的なものは、畳み込みニューラルネットワーク(CNN)、リカレントニューラルネットワーク(RNN)、そして最近ではGoogleのBERTのようなTransformerベースのネットワークの3つです。 CNNは主に画像認識アプリケーションに使用され、要するに行列処理問題である。RNNやBERTは音声認識などの問題によく使われ、GPUのようなSIMDプロセッサーではCNNモデルより効率が悪くなります。

FPGAロジックは、GPUのようなハードウェアにアルゴリズムを合わせるのではなく、ニューラルネットワークの処理要求に最適になるように再構成することができます。これは、バッチ数が少ない場合に特に重要で、バッチサイズを大きくすることは、GPUへの依存度が高いネットワークを処理するための解決策となることが多い。

Resnetは、多くの畳み込み層で構成される、よく引用されるニューラルネットワークである。しかし、これらの層のほとんどは、一般的な要件である1セル(1×1)しかないステンシルを使用しています。Resnetの最終層は、小さなステンシルサイズによって可能なデータの再利用量が減少するため、データ計算に対する重みの比率が非常に高くなります。これは、可能な限り低いレイテンシー、すなわちバッチサイズ1を達成しようとすると悪化します。最高のパフォーマンスを達成するためには、計算とメモリの帯域幅のバランスをとることが重要です。幸い、FPGA は DDR、HBM、GDDR、内蔵 SRAM メモリなど、さまざまな外部メモリをサポートしているため、適切なデバイスを選択すれば、ワークロードに応じてコンピュートに対する帯域幅の完璧な組み合わせを選択することができます。

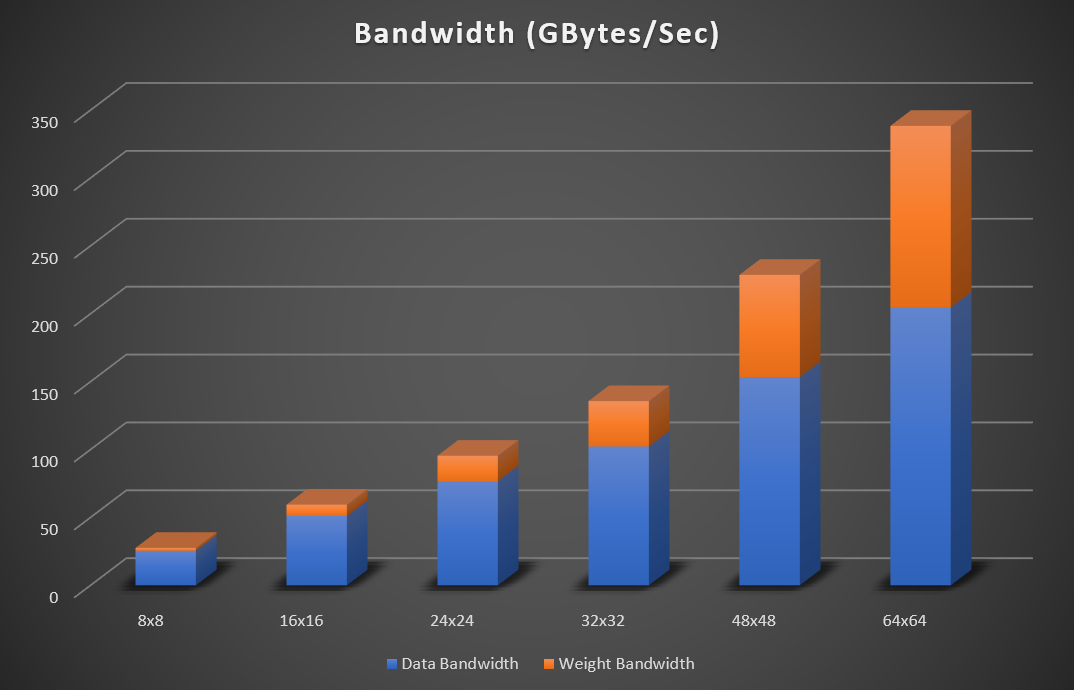

図4:Resnet(224×224)のマトリックスサイズが大きくなったときのピーク帯域要件(32bit浮動小数点データ)。

図4は、Resnet 50のマトリックスサイズが8×8、16×16、24×24、32×32、48×48、64×64の場合、ピーク帯域幅の必要量が増加していることを示している。帯域幅は、ウェイト、入力および出力データが外部メモリに読み書きされると仮定しています。一時的な蓄積の保存には、オンチップSRAMメモリが使用されます。ネットワークがFPGAのメモリ内に収まる場合は、メモリへの特徴データの読み書きを一貫して行う必要はない。この場合、外部データ帯域幅は無視できるほど小さくなります。int8実装の場合、必要な帯域幅の数値は4で割ることができます。

Bittware はベンダーにとらわれず、Intel、Xilinx、Achronix の FPGA 技術をサポートしています。すべてのFPGAベンダーは、低レイテンシーと低バッチ数の実装で優れた性能を発揮しますが、各デバイスにはコンフィギュラブルロジックのアプリケーションに微妙な違いがあります。

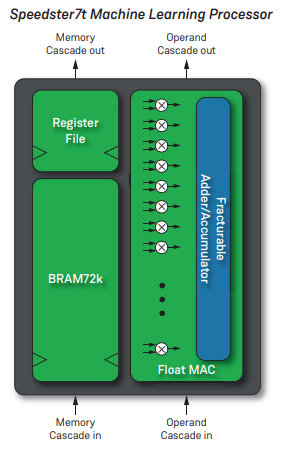

Achronix社の最新FPGAは、ニューラルネットワークの処理を高速化するために設計されたIPも備えています。このデバイスの各機械学習プロセッサ(MLP)は、4~24ビットの計算をサポートする32個の乗算アキュムレータ(MAC)を処理します。Bfloat16など、非標準の浮動小数点形式もサポートされています。Achronix MPLとIntelテンソル・コンポーネントの主な違いは、非連結SRAMと比較してより高いクロック速度を確保するために、SRAMメモリを密に結合していることです。

のことです。 Bittware S7t-VG6は、Speedster7t 、2,560MLPS、61TOps(int8またはbfloat16)の理論ピーク性能を持っています。

図5:Achronix MLP3

図6 :BittWare S7t-VG6

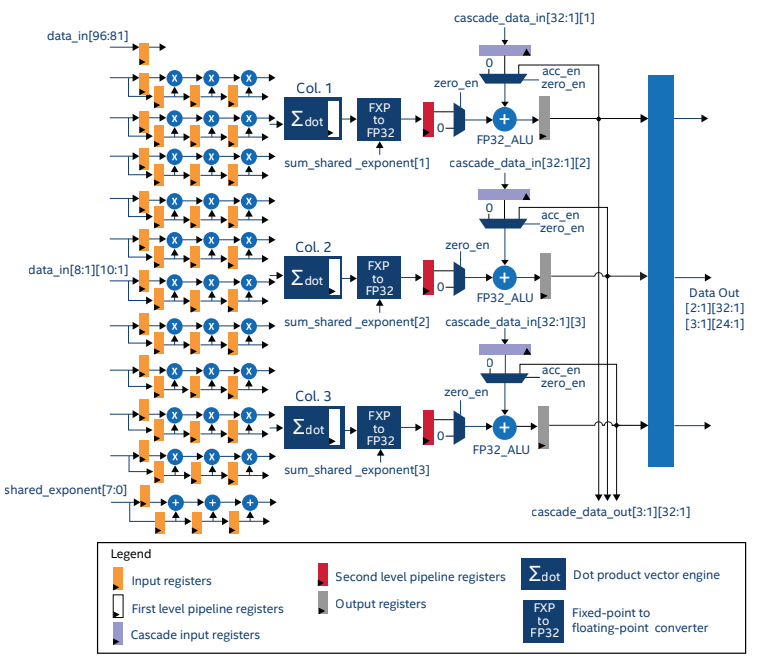

IntelStratix 10 NXは、IntelのFPGAとして初めて専用のテンソル演算ブロックを搭載した。テンソルIPは、10×3のデータブロックに対してテンソル演算を実行するように最適化されています(図5)。このIPは、int4、int8、Block FP12、Block FP16の各データ型を完全に活用して動作するように構成できます。

図7:Stratix 10 Tensor IP1

Startix10 NXデバイスの理論上のピークスループットを表1に示す。

また、Stratix 10 NXは、512GB/sの集約帯域幅を提供するHBM2メモリを搭載しており、利用可能なすべての処理に十分な帯域幅を確保することができます。

| 精密 | パフォーマンス |

| INT4 | 286 TOPS |

| INT8 | 143 TOPS |

| ブロックFP12 | 286 TFLOPS |

| ブロックFP16 | 143 TFLOPS |

表1:Stratix 10 理論上のピークスループット

Stratix 10 NXは、その中心的存在です。 Bittware 520NX アクセラレーターカードです。このカードは最大600Gbpsのボード間帯域幅を持ち、複数のカードをまとめて接続したり、センサーデータへの通信に利用することができます。

IntelAgilex シリーズはテンソルDSPコンポーネントを搭載していませんが、そのDSPはStratix 10 から改良され、より多くのデータ型をサポートし、低精度演算のスループットを向上させています。IntelAgilex MシリーズのResnet-50の理論性能は88 INT TOPS.2です。

図8 :BittWare 520NX

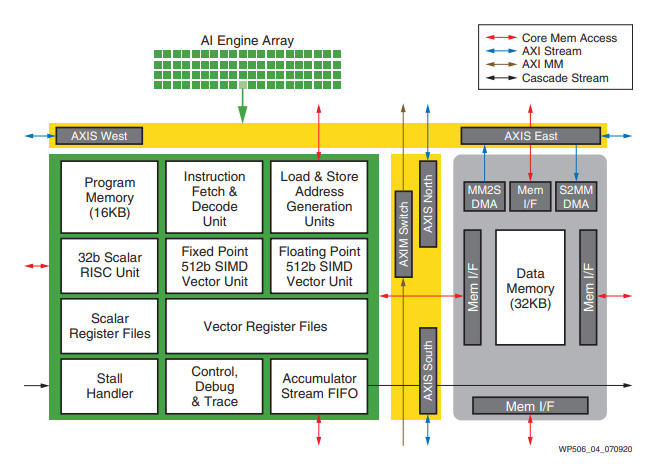

ザイリンクスのVersalデバイスには、FPGAのプログラマブルロジックに統合されていない独立したAIエンジンがあります。バーサルのAIエンジンはFPGAと密接に結合していますが、FPGAの他の部分とは独立して動作しています。データは、NOC(Network On Chip)を使用して、AIエンジンとFPGAロジックの間で受け渡されます。

図9:Versal AIエンジン

BittWare 現在、ACAP早期アクセスプログラムでは、AMD Xilinx®の7nm Versal Premium ACAPデバイスを搭載したダブルワイドPCIe Gen5アクセラレータカードなどのコンセプトがあります。詳しくは、Versalの情報ページをご覧ください。

AIエンジニアは、PyTorch、TensorFlow、Caffeなど、ニューラルネットワークを記述するために多くの異なる高レベルのツールを使用しています。幸い、AIコードをFPGAにコンパイルするAPIが用意されており、エンジニアは既存のツールフローを使い続けることができます。

Bittware は、この機能を持つパートナー企業を持っています:

EdgeCortix ダイナミック・ニューラル・アクセラレータ(DNA)は、Agilex FPGAを搭載したBittWare カードにおいて、高い計算能力、超低レイテンシー、スケーラブルな推論エンジンを備えた深層学習推論用の柔軟なIPコアです。

VASスイート メグコンピューティングのインテリジェントビデオ解析ソリューションは、TCOを考慮しながら、エンタープライズクラスのパフォーマンスで実用的な洞察を必要とするセキュリティおよびシステムインテグレータのためのソリューションです。

最新のFPGAは、低レイテンシー、小バッチサイズの推論を得意とする非常に高性能なAIプロセッサーです。他の処理要件と組み合わせることで、ユニークな能力を持つAIシステムを構築するための強力なプラットフォームとなります。システムの要求に応じて、あるFPGAベンダーが他のベンダーよりも適していることが証明されるかもしれません。BittWare 、電力、処理、IOの要件に基づいて適切なFPGAシステムを選択するために、お客様を支援する準備が整っています。

Atomic Rules社のPCIe Gen4データムーバーIPです。BittWareの PCIe Gen4 カードを使用して最大 220 Gb/s を達成し、標準 DMA よりも高い性能が必要な場合に開発チームの負担を軽減します。特徴DPDKおよびAXI規格、パケットやその他のデータフォーマットでの動作、最大400GbEまでのあらゆるラインレートでの動作。

記事 カスタマイズされた FPGA ソリューションを迅速に開発するための 2 つのアプローチBittWare カスタマイズされたソリューションのライフサイクル全体にわたってリスクを低減する方法 概要 データセンターにおける FPGA は、FPGA を使用しています。

BittWare SDK Software Development Kit forBittWare FPGA ハードウェアの概要BittWareの SDK はクロスプラットフォームのドライバ、ライブラリ、モジュール、ユーティリティのコレクションです。

PCIe FPGA Card 520NXStratix 10 AI-optimized FPGA with HBM2 AI-optimized for High-Bandwidth, Low-Latency AIアクセラレーション 旧製品のお知らせです:この製品は製造中止品です。