Bittiviare a molex company

# Agilex<sup>™</sup> FPGA card featuring 400G and Gen5 PCle

M-series FPGA with HBM2e supporting 1TBps total memory bandwidth

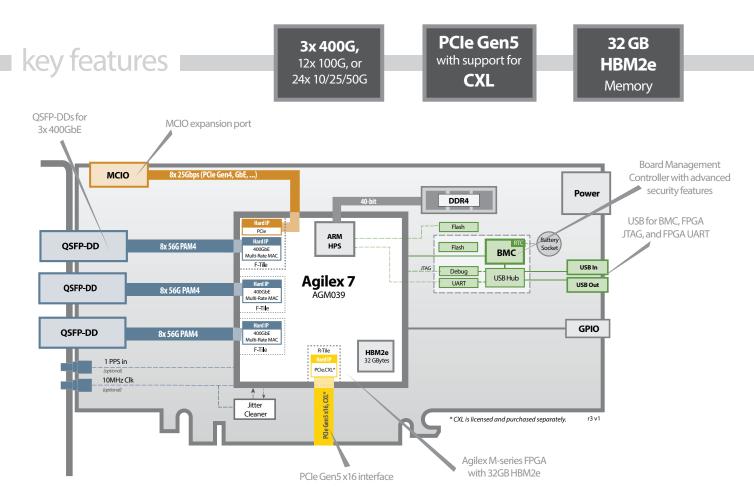

BittWare's IA-860m is an Altera Agilex<sup>™</sup> M-series FPGA card optimized for throughputand memory-intensive applications. The M-series FPGA features an extensive memory hierarchy including integrated high-bandwidth memory (HBM2e) and a hard memory Network-on-Chip (NoC) to maximize memory bandwidth. The IA-860m card provides a balance of I/O and memory leveraging the Agilex chip's unique tiling architecture with QSFP-DDs, PCIe Gen5 x16 with CXL support, and MCIO expansion port for a variety of applications.

The IA-860m has support for Intel oneAPI<sup>™</sup>, which enables an abstracted development flow for dramatically simplified code re-use across multiple architectures.

### **Board Specifications**

| FPGA              | <ul> <li>Altera Agilex 7 M-Series: AGM039 (default)         <ul> <li>Package: R47A</li> <li>32GB HBM2e</li> <li>Core speed grade -2; XCVR speed grade -1</li> <li>CXL with XCVR speed grade -1 (CXL IP is licensed and purchased separately)</li> <li>FPGA includes ARM HPS</li> </ul> </li> </ul>                                                                                      |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARM HPS           | <ul> <li>Dedicated 40-bit DDR4</li> <li>Dedicated Flash memory for booting ARM</li> <li>Optional 1GbE interface (contact BittWare)</li> </ul>                                                                                                                                                                                                                                           |

| On-board Flash    | 2Gbit Flash memory for booting FPGA                                                                                                                                                                                                                                                                                                                                                     |

| Host interface    | <ul> <li>x16 PCIe Gen5 interface direct to FPGA</li> <li>CXL support (CXL IP is licensed and purchased separately)</li> </ul>                                                                                                                                                                                                                                                           |

| QSFP-DD cages     | <ul> <li>3x QSFP-DD cages on front panel connected<br/>directly to FPGA via 24 transceivers</li> <li>User programmable low jitter clocking supporting<br/>10/25/40/100/200/400GbE</li> <li>Each QSFP-DD can be independently clocked</li> <li>Jitter cleaner for network recovered clocking</li> <li>Multi-rate hard MAC+FEC</li> <li>Fully backward compatible with QSFP28s</li> </ul> |

| MCIO              | x8 connector supporting 2x Gen4 x4 root complexes                                                                                                                                                                                                                                                                                                                                       |

| GPIO              | • 4x GPIO                                                                                                                                                                                                                                                                                                                                                                               |

| External clocking | <ul> <li>1 PPS and 10MHz ref clk front panel inputs<br/>(optional)</li> </ul>                                                                                                                                                                                                                                                                                                           |

| USB               | USB access to BMC, USB-JTAG, USB-UART                                                                                                                                                                                                                                                                                                                                                   |

|                   |                                                                                                                                                                                                                                                                                                                                                                                         |

| Board<br>Management<br>Controller | <ul> <li>Power sequencing and reset</li> <li>Voltage, current, temperature monitoring <ul> <li>Protection shut-down</li> </ul> </li> <li>Clock configuration</li> <li>Low bandwidth BMC-FPGA comms with SPI link</li> <li>USB 2.0</li> <li>PLDM support</li> <li>Card-level security <ul> <li>BMC Root of Trust</li> <li>BMC and FPGA secure boot</li> <li>BMC and FPGA secure upgrade</li> <li>Key management</li> </ul> </li> </ul> |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cooling                           | <ul><li>Standard: dual-width passive heatsink</li><li>Optional: dual-width liquid cooling</li></ul>                                                                                                                                                                                                                                                                                                                                   |

| Electrical                        | <ul> <li>On-board power derived from PCIe slot 12V and<br/>12-pin AUX power connector</li> <li>Power dissipation is application dependent</li> <li>Typical max power consumption TBD</li> </ul>                                                                                                                                                                                                                                       |

| Environmental                     | <ul> <li>Operating temperature: 5°C to 35°C (passive heatsink)</li> </ul>                                                                                                                                                                                                                                                                                                                                                             |

| Quality                           | <ul> <li>Manufactured to IPC-A-610 Class 2</li> <li>RoHS compliant</li> <li>CE, FCC, UKCA &amp; ICES approvals</li> </ul>                                                                                                                                                                                                                                                                                                             |

| Form factor                       | <ul> <li>Standard-height, full-length, dual-slot PCIe card</li> <li>111.15mm x 312.00mm (4.376in x 12.283in)</li> </ul>                                                                                                                                                                                                                                                                                                               |

## **Development Tools**

| System<br>development   | BittWare SDK including PCIe driver, libraries, and board monitoring utilities                                                                          |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Application development | Supported design flows - Altera FPGA oneAPI Base<br>Toolkit, Altera High-Level Synthesis (C/C++) and Quar-<br>tus Prime Pro (HDL, Verilog, VHDL, etc.) |

# Accessory Cables

Access to USB and JTAG requires accessory cables. Cables are sold separately.

| USB In cable    | Pico-lock to USB A cable<br>BittWare part number: RS-PL05-UAP-83<br>Designed for deployment in servers |

|-----------------|--------------------------------------------------------------------------------------------------------|

| USB Out cable   | Pico-lock to Pico-lock<br>BittWare part number: RS-PL05-PL05-24                                        |

| JTAG-only cable | Pico-lock to JTAG cable<br>BittWare part number: RS-PL06-JTB-13<br>Recommended for development         |

#### Safety & Compliance

- FCC (USA) 47CFR15.107 / 47CFR15.109

- CE (Europe) EN55032:2015 / EN55035:2017 / EN61000-3-2:2019 + A1:2021 / EN610003-3:2013

- UKCA (United Kingdom) BS EN55032:2015 / BS EN55035:2017 / BS EN61000-3-2:2019 +

- ICES (Canada) ICES-003 Issue

## To learn more, visit www.BittWare.com

r3 v2 | last revised 2025.06.05

© BittWare 2025

Agilex is a trademark of Intel Corp. All other products are the trademarks or registered trademarks of their respective holders.