**250-SoC** DAA and NVMe-oF

# **Directly Attached Accelerator & NVMe-over-Fabric**

Reliable transport of NVMe frames with low latency and high throughput

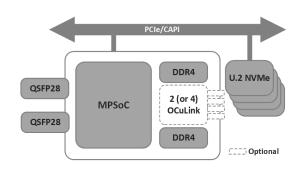

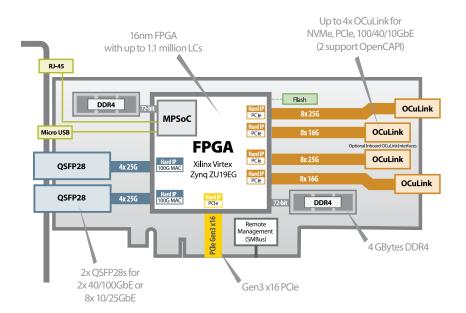

The 250-SoC enables the creation of remote, disaggregated storage or Ethernet Just-a-Bunch-of-Flash (EJBOF) to dramatically reduce the storage cost, footprint and power within data centers. The 250-SoC features a Xilinx Zynq UltraScale+ MPSoC device featuring both programmable logic and 64-bit ARM processors. This powerful, feature-rich device coordinates data transfer between two 100GbE network ports, on-board DDR4 memory and a PCle Gen 3 host interface.

key features

2x 100GbE via 2 QSFP28 Ideal for **NVMe** storage arrays

ZU19EG MPSoC: **64-bit Cortex A53 ARM** Zynq UltraScale+

## **Accelerating High Level Design**

- Vivado HLx Editions supply design teams with the tools and methodology needed to leverage C-based design and optimized reuse

- Includes IP sub-system reuse, integration automation and accelerated design closure

- When coupled with the UltraFast™ High-Level Productivity Design Methodology Guide, this unique combination is proven to accelerate productivity

- It enables designers to work at a high level of abstraction while facilitating design

THIS A.

THE SECTION OF THE SE

## **Additional Services**

Take advantage of BittWare's range of design, integration, and support options

**Customization**

Additional specification options or accessory boards to meet your exact needs.

#### **Server Integration**

Available pre-integrated in our <u>TeraBox servers</u> in a range of configurations.

#### **IP and Solutions**

Our portfolio of IP and solutions reduce risk for development and deployment.

## **Service and Support**

BittWare Developer Site provides online documentation and issue tracking.

## **Specifications**

| Specification                                                    | 5                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPGA                                                             | Xilinx Zynq UltraScale+     ZU19EG FFVD1760 package     Core speed grade -2     Application ARM: Quad-core Cortex-A53 MP-Core 1.5GHz     Real-Time ARM: Dual-core Cortex-R5 MPCore 600MHz     Graphics Processor: Mali-400 MP2     Contact BittWare for other MPSoC options |

| On-board DDR4<br>SDRAM                                           | DDR4 SDRAM FPGA Fabric Memory     One 4GB bank of DDR4 SDRAM x72 bits     Transfer Rate: 2400 MT/s     DDR4 SDRAM MPSoC Memory     One 4GB bank of DDR4 SDRAM x72 bits     Transfer rate: 2400 MT/s                                                                         |

| Host interface                                                   | <ul> <li>x16 mechanical PCle Gen3 capable</li> <li>Configurable as x16 up to Gen3, or two x8 PCl in bifurcated slots</li> </ul>                                                                                                                                             |

| QSFP cages                                                       | <ul> <li>2 front panel 4-25Gbps-lane QSFP28 cages</li> <li>User programmable low jitter clocking supporting 10/25/40/100GbE</li> <li>Each QSFP28 can be independently clocked</li> </ul>                                                                                    |

| OCuLink                                                          | <ul> <li>1 back panel 8-25Gbps-lane OCuLink connector</li> <li>1 back panel 8-16Gbps-lane OCuLink connector</li> <li>Flexible configuration: NVMe, PCle, 10/40/100GbE, OpenCAPI</li> <li>2 additional optional 8-lane OCuLink connectors (25 &amp; 16Gbps)</li> </ul>       |

| Board control<br>(front panel)                                   | RJ45 1GbE access to the ARM processor     USB connector for UART to ARM processor                                                                                                                                                                                           |

| Datacenter<br>Deployment,<br>Health<br>Monitoring &<br>Reporting | <ul> <li>On-board power, voltage and temperature monitoring</li> <li>Field flash update via software</li> <li>SMBus controlled anti-bricking, fallback and multi-boot</li> <li>SMBus access to unique board data and temperature sensor</li> </ul>                          |

| Cooling       | Active and passive heatsink options                                                                                                                                |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrical    | <ul> <li>On-card power derived from PCIe slot supplies</li> <li>Power dissipation is application dependent</li> <li>Typical FPGA power consumption ~50W</li> </ul> |

| Environmental | Operating temperature: 5°C to 35°C                                                                                                                                 |

| Quality       | Manufactured to IPC-A-610 Class 2     RoHS compliant                                                                                                               |

| Form factor   | <ul> <li>Half-height, half-length PCle board</li> <li>Full-height PCl bracket option</li> <li>68.90mm x 167.65mm (2.713in x 6.600in)</li> </ul>                    |

### **Development Tools**

| FPGA<br>development     | BIST - Built-In Self-Test for CentOS 7 provided with source code (pinout, gateware, PCIe driver and host test application) |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Application development | Xilinx Tools - Vivado Design Suite HLx Editions: HDL and C/C++ with HLS                                                    |

### **Deliverables**

- 250-SoC FPGA board

- Built-In Self-Test (BIST)

- 1-year access to online Developer Site

- 1-year hardware warranty

## To learn more, visit www.BittWare.com

Rev 2023.01.30 | January 2023

© BittWare 2023

UltraScale, Virtex, and Vivado are registered trademarks of Xilinx Corp. All other products are the trademarks or registered trademarks of their respective holders.